Статическая память (SRAM) обычно применяется в качестве кэш-памяти второго уровня для кэширования основного объема ОЗУ. Статическая память выполняется обычно на основе ТТЛ-. КМОП- или БиКМОП-микросхем и по способу доступа к данным может быть как асинхронной, так и синхронной. Асинхронным называется доступ к данным, который можно осуществлять в произвольный момент времени. Асинхронная SRAM применялась на материнских платах для третьего - пятого поколений процессоров. Время доступа к ячейкам такой памяти составляло от 15 (33 МГц) до 8 нс (66 МГц).

Синхронная память обеспечивает доступ к данным не в произвольные моменты времени, а синхронно с тактовыми импульсами. В промежутках между ними память может готовить для доступа следующую порцию данных. В большинстве материнских плат пятого поколения используется разновидность синхронной памяти - пакетно-конвейерная SRAM (Pipelined Burst SRAM), для которой типичное время одиночной операции чтения/записи составляет 3 такта, а групповая операция занимает 3-1-1-1 такта при первом обращении и 1-1-1-1 при последующих обращениях, что обеспечивает ускорение доступа более чем на 25 %.

Async SRAM (Асинхронная статическая память). Это кэш-память, которая используется в течение многих лет с тех пор, как появился первый 386-й компьютер с кэш-памятью второго уровня. Обращение к ней производится быстрее, чем к DRAM, и могут, в зависимости от скорости ЦП, использоваться варианты с доступом за 20, 15 или 10 нс (чем меньше время обращения к данным, тем быстрее память и тем короче может быть пакетный доступ к ней). Тем не менее, как видно из названия, эта память является недостаточно быстрой для синхронного доступа, что означает, что для обращения ЦП все-таки требуется ожидание, хотя и меньшее, чем при использовании DRAM.

SyncBurst SRAM (Синхронная пакетная статическая память). При частотах шины, не превышающих 66 МГц, синхронная пакетная SRAM является наиболее быстрой из существующих видов памяти. Причина этого в том, что, если ЦП работает на не слишком большой частоте, синхронная пакетная SRAM может обеспечить полностью синхронную выдачу данных, что означает отсутствие задержки при пакетном чтении ЦП 2-1-1-1. Когда частота ЦП становится больше 66 МГц, синхронная пакетная SRAM не справляется с нагрузкой и выдает данные пакетами по 3-2-2-2, что существенно медленнее, чем при использовании конвейерной пакетной SRAM. К недостаткам относится и то, что синхронная пакетная SRAM производится меньшим числом компаний и поэтому стоит дороже.

Синхронная пакетная SRAM имеет время адрес/данные от 8,5 до 12 не.

РВ SRAM (Конвейерная пакетная статическая память). Конвейер - распараллеливание операций SRAM с использованием входных и выходных регистров. Заполнение регистров требует дополнительного начального цикла, но, будучи заполненными, регистры обеспечивают быстрый переход к следующему адресу за то время, пока по текущему адресу считываются данные.

Благодаря этому такая память является наиболее быстрой кэш-памятью для систем с производительностью шины более 75 МГц. РВ SRAM может работать при частоте шины до 133 МГц. Она, кроме того, работает ненамного медленнее, чем синхронная пакетная SRAM при использовании в медленных системах: она выдает данные пакетами по 3-1-1-1 все время. Время адрес/данные составляет от 4,5 до 8 нс.

1-Т SRAM. Традиционные конструкции SRAM используют для запоминания одного разряда (ячейки) статический триггер. Для реализации одной такой схемы на плате должно быть размещено от четырех до шести транзисторов (4-Т, 6-Т SRAM). Фирма Monolithic System Technology (MoSys) объявила о создании нового типа памяти, в которой каждый разряд реализован на одном транзисторе (1-Т SRAM). Фактически здесь применяется технология DRAM, поскольку приходится осуществлять периодическую регенерацию памяти. Однако интерфейс с памятью выполнен в стандарте SRAM, при этом циклы регенерации скрыты от контроллера памяти. Схемы 1-Т позволяют снизить размер кремниевого кристалла на 50-80 % по сравнению с аналогичными для SRAM, а потребление электроэнергии - на 75 %.

Системы видеопамяти

Известны следующие типы видеопамяти (табл. 2.1, здесь отражены также некоторые из вышеперечисленных универсальных сиетем памяти). VRAM (Video RAM - видеоОЗУ) - так называемая двухпортовая DRAM. Этот тип памяти обеспечивает доступ к данным со стороны сразу двух устройств, т. е. есть возможность одновременно писать данные в какую-либо ячейку памяти и одновременно с этим читать данные из какой-нибудь соседней ячейки. За счет этого позволяет совмещать во времени вывод изображения на экран и его обработку в видеопамяти, что сокращает задержки при доступе и увеличивает скорость работы.

WRAM (Window RAM) - вариант VRAM, с увеличенной на -25 % пропускной способностью и поддержкой некоторых часто применяемых функций, таких как отображение шрифтов, перемещение блоков изображения и т. п. Применяется практически только на акселераторах фирм Matrox и Number Nine, поскольку требует специальных методов доступа и обработки данных, наличие всего одного производителя данного типа памяти (Samsung) сильно сократило возможности ее использования. Видеоадаптеры, построенные с использованием данного типа памяти, не имеют тенденции к падению производительности при установке больших разрешений и частот обновления экрана.

SGRAM (Synchronous Graphics RAM - синхронное графическое ОЗУ) - вариант DRAM с синхронным доступом. В принципе, работа SGRAM полностью аналогична SDRAM, но дополнительно поддерживаются еще некоторые специфические функции, типа блоковой и масочной записи. В отличие от VRAM и WRAM, SGRAM является однопортовой, однако может открывать две страницы памяти как одну, эмулируя двухпортовость других типов видеопамяти.

MDRAM (Multibank DRAM - многобанковое ОЗУ) - вариант DRAM, разработанный фирмой MoSys, организованный в виде множества независимых банков объемом по 32 Кбайт каждый, работающих в конвейерном режиме, и использующий распараллеливание операций доступа к данным между большим количеством банков памяти.

РЕСПУБЛИКА КАЗАХСТАН

УНИВЕРСИТЕТ "ТУРАН"

Кафедра "информационных технологий"

тема:"Статическая память"

Выполнил: Айнакулов Д.А. 3курс, "ИС" 9 гр. Проверила: ЗиятбековаГ.З.

Алматы 2009 г.

1. Введение

2. Статическая память

4. Типы статической памяти

5. Заключение

1. Введение

Персональные компьютеры PC сегодня стали незаменимыми помощниками человека во всех без исключения сферах человеческой деятельности. На компьютерах рассчитывают заработную плату и объем урожая, рисуют графики движения товаров и изменения общественного мнения, проектируют атомные реакторы и т.д.

Слово "компьютер" означает "вычислитель". Потребность в автоматизации обработки данных, в том числе вычислений, возникла очень давно. В настоящее время индустрия производства компьютерного железа и программного обеспечения является одной из наиболее важных сфер экономики развитых и развивающихся стран. Причины стремительного роста индустрии персональных компьютеров: невысокая стоимость; сравнительная выгодность для многих деловых применений; простота использования; возможность индивидуального взаимодействия с компьютеров без посредников и ограничений; высокие возможности по переработке, хранению и выдаче информации; высокая надежность, простота ремонта и эксплуатации; компьютерное железо адаптивно к особенностям применения компьютеров; наличие программного обеспечения, охватывающего практически все сферы человеческой деятельности, а также мощных систем для разработки нового программного обеспечения. Мощность компьютеров постоянно увеличивается, а область их применения постоянно расширяется. Компьютеры могут объединяться в сети, что позволяет миллионам людей легко обмениваться информацией с компьютерами, находящимися в любой точке земного шара. Так что же представляет собой это уникальное человеческое изобретение? Первый признак, по которому разделяют компьютеры, - платформа. Можно выделить две основные платформы ПК: Платформа IBM – совместимых компьютеров включает в себя громадный спектр самых различных компьютеров, от простеньких домашних персоналок до сложных серверов. Именно с этим типом платформ обычно сталкивается пользователь. Кстати, совершенно не обязательно, что лучшие IBM – совместимые компьютеры изготовлены фирмой IBM – породивший этот стандарт "голубой гигант" сегодня лишь один из великого множества производителей ПК. Платформа Apple - представлена довольно популярными на Западе компьютерами Macintosh. Они используют своё, особое программное обеспечение, да и "начинка" их существенно отличается от IBM. Обычно IBM-совместимые ПК состоят из трех частей (блоков): системного блока; монитора (дисплея); клавиатуры (устройства, позволяющего вводить символы в компьютер). Развитие электронной промышленности осуществляется такими быстрыми темпами, что буквально через один год, сегодняшнее "чудо техники" становится морально устаревшим вследствие того, что компьютерное железо постоянно модифицируется, появляется новое программное обеспечение. Однако принципы устройства компьютера остаются неизменными еще с того момента, как знаменитый математик Джон фон Нейман в 1945 году подготовил доклад об устройстве и функционировании универсальных вычислительных устройств.

2. Статическая память

Статическая память, или SRAM (Statistic RAM) является наиболее производительным типом памяти. Микросхемы SRAM применяются для кэширования оперативной памяти, в которой используются микросхемы динамической памяти, а также для кэширования данных в механических устройствах хранения информации, в блоках памяти видеоадаптеров и т. д. Фактически, микросхемы SRAM используются там, где необходимый объем памяти не очень велик, но высоки требования к быстродействию, а раз так, то оправдано использование дорогостоящих микросхем. В персональных компьютерах с процессорами, у которых не было интегрированной на кристалле кэш-памяти второго уровня, всегда использовались микросхемы SRAM внешнего кэша. Для удешевления системных плат и возможности их модернизации производители системных плат с процессорами 486 и первых поколений Pentium устанавливали специальные кроватки (разъемы для микросхем с DIP-корпусом), в которые можно было устанавливать различные микросхемы SRAM, отличающиеся как по быстродействию и объему памяти, так и различной разрядностью. Для конфигурирования памяти на системной плате предусматривался набор джамперов. Для справки прямо на системной плате краской наносилась информация об установке джамперов, например, как показано в табл.(в колонках JS1 и JS2 указаны номера контактов, которые надо замкнуть перемычками).

Пример таблицы конфигурирования кэш-памяти на системной плате

| Size | SRAM | JS1 | JS2 |

| 256 К | 32x8 | 1-2 | 1-2 |

| 512 К | 64x8 | 2-3 | 1-2 |

| 1 М | 128x8 | 2-3 | 2-3 |

Отметим, что изменением конфигурации кэш-памяти занимались только тогда, когда выходила из строя какая-либо микросхема кэш-памяти. В остальных случаях изменять положение джамперов не рекомендовалось. В дальнейшем, по мере разработки более совершенных микросхем SRAM, они непосредственно припаивались на системную плату в количестве 1, 2 или 4 штук. На системных платах, которые выпускаются в настоящее время, микросхемы SRAM используются, в основном, только для кэширования ввода/вывода и других системных функций.

3. Устройство матрицы статической памяти

Подобно ячейкам динамической, триггеры объединяются в единую матрицу, состоящую из строк (row) и столбцов (column), последние из которых так же называются битами (bit).

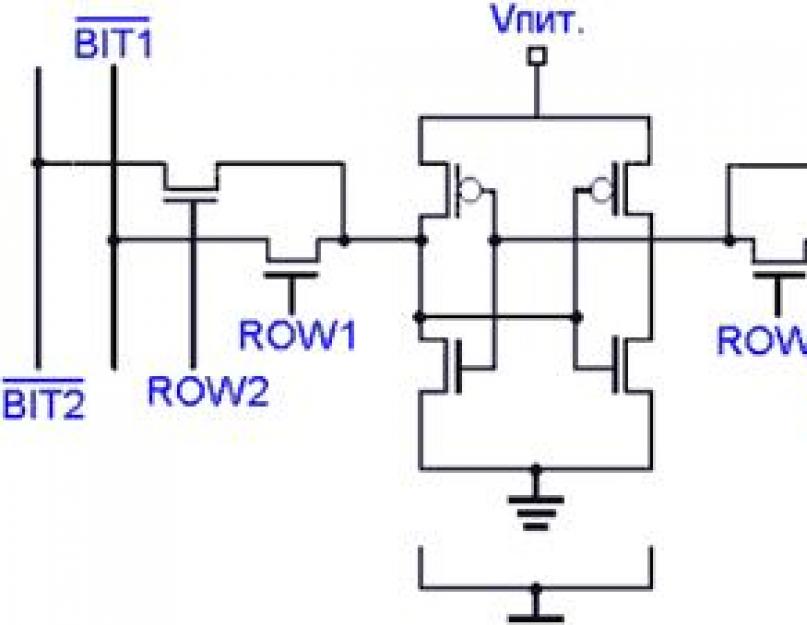

В отличии от ячейки динамической памяти, для управления которой достаточно всего одного ключевого транзистора, ячейка статической памяти управляется как минимум двумя. Это не покажется удивительным, если вспомнить, что триггер, в отличии от конденсатора, имеет раздельные входы для записи логического нуля и единицы соответственно. Таким образом, на ячейку статической памяти расходуется целых восемь транзисторов (см. рис.1) - четыре идут, собственно, на сам триггер и еще два - на управляющие "защелки".

Рис. 1. Устройство 6-транзистроной одно-портовой ячейки SRAM-памяти

Причем, шесть транзисторов на ячейку - это еще не предел! Существуют и более сложные конструкции! Основной недостаток шести транзисторной ячейки заключается в том, что в каждый момент времени может обрабатываться всего лишь одна строка матрицы памяти. Параллельное чтение ячеек, расположенных в различных строках одного и того же банка невозможно, равно как невозможно и чтение одной ячейки одновременно с записью другой.

Этого ограничения лишена многопортовая память. Каждая ячейка многопортовой памяти содержит один-единственный триггер, но имеет несколько комплектов управляющих транзисторов, каждый из которых подключен к "своим" линиям ROW и BIT, благодаря чему различные ячейки матрицы могут обрабатываться независимо. Такой подход намного более прогрессивен, чем деление памяти на банки. Ведь, в последнем случае параллелизм достигается лишь при обращении к ячейкам различных банков, что не всегда выполнимо, а много портовая память допускает одновременную обработку любых ячеек, избавляя программиста от необходимости вникать в особенности ее архитектуры.

Наиболее часто встречается двух - портовая память, устройство ячейки которой изображено на рис. 2. (внимание! это совсем не та память которая, в частности, применяется в кэше первого уровня микропроцессоров Intel Pentium). Нетрудно подсчитать, что для создания одной ячейки двух - портовой памяти расходуется аж восемь транзисторов. Пусть емкость кэш-памяти составляет 32 Кб, тогда только на одно ядро уйдет свыше двух миллионов транзисторов!

Рис. 2. Устройство 8-транзистроной двух портовой ячейки SRAM-памяти

Рис. 3. Ячейка динамической памяти воплощенная в кристалле

4. Типы статической памяти

Существует как минимум три типа статической памяти: асинхронная, синхронная и конвейерная. Все они практически ничем не отличаются от соответствующих им типов динамической памяти.

Асинхронная статическая память

Асинхронная статическая память работает независимо от контроллера и потому, контроллер не может быть уверен, что окончание цикла обмена совпадет с началом очередного тактового импульса. В результате, цикл обмена удлиняется по крайней мере на один такт, снижая тем самым эффективную производительность. "Благодаря" последнему обстоятельству, в настоящее время асинхронная память практически нигде не применяется (последними компьютерами, на которых она еще использовались в качестве кэша второго уровня, стали "трешки" - машины, построенные на базе процессора Intel 80386).

Синхронная статическая память

Синхронная статическая память выполняет все операции одновременно с тактовыми сигналами, в результате чего время доступа к ячейке укладывается в один-единственный такт. Именно на синхронной статической памяти реализуется кэш первого уровня современных процессоров.

Конвейерная статическая память

Конвейерная статическая память представляет собой синхронную статическую память, оснащенную специальными "защелками", удерживающими линии данных, что позволяет читать (записывать) содержимое одной ячейки параллельно с передачей адреса другой.

Так же, конвейерная память может обрабатывать несколько смежных ячеек за один рабочий цикл. Достаточно передать лишь адрес первой ячейки пакета, а адреса остальных микросхема вычислит самостоятельно, - только успевай подавать (забирать) записывание (считанные) данные!

За счет большей аппаратной сложности конвейерной памяти, время доступа к первой ячейке пакета увеличивается на один такт, однако, это практически не снижает производительности, т.к. все последующие ячейки пакета обрабатываются без задержек.

Конвейерная статическая память используется в частности в кэше второго уровня микропроцессоров Pentium-II и ее формула выглядит так: 2-1-1-1.

5. Заключение

История создания статической памяти уходит своими корнями в глубину веков. Память первых релейных компьютеров по своей природе была статической и долгое время не претерпевала практически никаких изменений - менялась лишь элементарная база: на смену реле пришли электронные лампы, впоследствии вытесненные сначала транзисторами, а затем TTL- и CMOS-микросхемами: но идея, лежащая в основе статической памяти, была и остается прежней...

К сожалению, между человеком и компьютером стоит трудно преодолимая для многих преграда - различия в способах ввода, обработки и вывода информации. Соответственно, специалистов, которые отлично разбираются в компьютерном железе, не так много, и они всегда на вес золота.

Так как многие любят собирать компьютер самостоятельно, на сайте приведены самые важные сведения о способах сборки и настройки системного блока. Ведь чтобы собрать что-либо толковое, полезное для использования, надо достаточно ясно представлять, что собираешь, для какой области применения и, конечно, из каких узлов. Примерно так можно сформулировать все многообразие вопросов, возникающих перед человеком, когда он решит не купить готовый компьютер, а собрать его собственными руками выбирая то "железо", которое ему необходимо. В связи со стремительным развитие компьютерных технологий а также вследствие того, что компьютерное железо постоянно модифицируется и в прадажу постоянно поступают новые модели, некоторая информация, приведенная на сайте, постепенно теряет свою актуальность.

Список использованной литературы

1. Информатика. Учебное пособие /Ломтадзе В.В., Шишкина Л.П. – Иркутск: ИрГТУ, 1999. – 116с.

2. Информатика. Учебное пособие /Под ред. В.Г. Кирия. – Иркутск: ИрГТУ,1998 часть 2. – 382с.

3. Макарова Н.В. Информатика.- Москва: Финансы и статистика, 1997.

4. Горев А., Ахаян Р., Макашарипов С. Эффективная работа с СУБД. СПб.: Питер, 1997.

Общие сведения. Статическая память (Static Random Access Memory – SRAM) способна сколь угодно долго хранить данные в отсутствие обращений (при наличии питающего напряжения), т.е. в статическом режиме. Ячейки статической памяти строятся на элементах с двумя устойчивыми состояниями (на бистабильных ячейках или триггерах). По сравнению с динамическими емкостными элементами памяти они проще в управлении и не требуют регенерации, однако являются более сложными в схемном отношении и занимают больше места на кристалле. Быстродействие и энергопотребление статической памяти определяются технологией изготовления и схемотехникой запоминающих ячеек. Самая экономичная КМОП-память (CMOS Memory) пригодна для длительного хранения данных при питании от маломощной батареи. Она применяется в памяти конфигурации персональных компьютеров. Время доступа КМОП-памяти составляет более 100 нс. Самая быстродействующая статическая память имеет время доступа в несколько наносекунд (и даже десятых долей наносекунды). Такая память способна функционировать на частоте системной шины совместно с процессором, не требуя от него тактов ожидания.

Типовой объем памяти современных микросхем SRAM достигает 1 Мбит и более. Существуют три разновидности микросхем статической памяти: Async SRAM, Sync Burst SRAM и Pipelined Burst SRAM. Относительно высокая удельная стоимость хранения данных при низкой плотности упаковки не позволяет использовать SRAM в качестве основной памяти компьютеров.

Во избежание увеличения стоимости в компьютерах устанавливается небольшой объем высокоскоростной статической памяти SRAM, которая используется в качестве кэша. Кэш-память способна работать на тактовых частотах, близких или равных тактовым частотам процессора. Поэтому она непосредственно используется процессором при чтении и записи, что позволяет сократить количество его простоев и увеличить быстродействие компьютера в целом. Контроллер кэша предугадывает потребности процессора в данных и предварительно загружает необходимые данные в высокоскоростную кэш-память. При выдаче процессором адреса памяти данные передаются не из медленной оперативной памяти, а из кэша.

Для сокращения времени ожидания и простоев процессора при считывании данных из низкоскоростной оперативной памяти в современных компьютерах предусмотрено до трех уровней кэша. При этом кэш-память первого и второго уровней может располагаться на одном кристалле с процессором. Использование синхронной работы с процессором и конвейерного пакетного режима сопутствует повышению быстродействия и эффективности кэш-памяти. Возможности и эффективность кэш-памяти предопределяет контроллер, который располагается в микросхемах (обычно North Bridge) системной логики или на плате процессора.

Таким образом, к основным особенностям статических ОЗУ следует отнести:

- способность при включенном компьютере сколь угодно долго хранить данные (информацию) в отсутствие обращений. Такая способность обеспечивается бистабильными ячейками памяти с двумя устойчивыми состояниями, которые выполняются на биполярных или КМОП-структурах;

- сравнительно высокое быстродействие микросхем на биполярных структурах (время доступа составляет единицы наносекунд), позволяющее работать синхронно с процессорами на частотах выше 500 МГц;

- низкое энергопотребление КМОП-микросхем, обеспечивающее длительное хранение параметров системы ввода-вывода (BIOS);

- сравнительно большие габариты микросхем и высокая стоимость , что связано с большим числом транзисторов и кластеризованным их размещением (используются кластеры из шести транзисторов);

- типовой объем памяти микросхем SRAM достигает 1 Мбит и более;

- основная область применения – кэш-память и память конфигурации компьютера.

Существует два типа статических переменных:

- глобальные переменные

- это переменные, определенные вне функций

, в описании которых отсутствует слово static

. Обычно описания

глобальных переменных, включающие слово extern

, выносятся в заголовочные файлы (h-файлы). Слово extern

означает, что переменная описывается, но не создается в данной точке программы. Определения

глобальных переменных, т.е. описания без слова extern

, помещаются в файлы реализации (c-файлы или cpp-файлы). Пример: глобальная переменная maxind

описывается дважды:

- в h-файле с помощью строки

extern int maxind;

это описание сообщает о наличии такой переменной, но не создает эту переменную! - в cpp-файле с помощью строки

int maxind = 1000;

это описание создает переменную maxind и присваивает ей начальное значение 1000 . Заметим, что стандарт языка не требует обязательного присвоения начальных значений глобальным переменным, но, тем не менее, это лучше делать всегда, иначе в переменной будет содержаться непредсказуемое значение (мусор, как говорят программисты). Инициализация всех глобальных переменных при их определении - это правило хорошего стиля.

- в h-файле с помощью строки

- статические переменные

- это переменные, в описании которых присутствует слово static

. Как правило, статические переменные описываются вне функций

. Такие статические переменные во всем подобны глобальным, с одним исключением: область видимости статической переменной ограничена одним файлом, внутри которого она определена, - и, более того, ее можно использовать только после ее описания, т.е. ниже по тексту. По этой причине описания статических переменных обычно выносятся в начало файла. В отличие от глобальных переменных, статические переменные никогда

не описываются в h-файлах (модификаторы extern

и static

конфликтуют между собой).

Совет: используйте статические переменные, если нужно, чтобы они были доступны только для функций, описанных внутри одного и того же файла

. По возможности не применяйте в таких ситуациях глобальные переменные, это позволит избежать конфликтов имен при реализации больших проектов, состоящих из сотен файлов.

- Статическую переменную можно описать и внутри функции, хотя обычно так никто не делает. Переменная размещается не в стеке, а в статической памяти, т.е. ее нельзя использовать при рекурсии, а ее значение сохраняется между различными входами в функцию. Область видимости такой переменной ограничена телом функции, в которой она определена. В остальном она подобна статической или глобальной переменной.

Заметим, что ключевое слово static

в языке Си используется для двух различных целей:

- как указание типа памяти: переменная располагается в статической памяти, а не в стеке;

- как способ ограничить область видимости переменной рамками одного файла (в случае описания переменной вне функции).

- Статическую переменную можно описать и внутри функции, хотя обычно так никто не делает. Переменная размещается не в стеке, а в статической памяти, т.е. ее нельзя использовать при рекурсии, а ее значение сохраняется между различными входами в функцию. Область видимости такой переменной ограничена телом функции, в которой она определена. В остальном она подобна статической или глобальной переменной.

Заметим, что ключевое слово static

в языке Си используется для двух различных целей:

- Слово static

может присутствовать и в заголовке функции. При этом оно используется только для того, чтобы ограничить область видимости имени функции рамками одного файла. Пример:

static int gcd(int x, int y); // Прототип ф-ции. . . static int gcd(int x, int y) { // Реализация. . . }

Совет: используйте модификатор static в заголовке функции, если известно, что функция будет вызываться лишь внутри одного файла. Слово static должно присутствовать как в описании прототипа функции, так и в заголовке функции при ее реализации.

Стековая, или локальная, память

Локальные, или стековые, переменные - это переменные, описанные внутри функции . Память для таких переменных выделяется в аппаратном стеке, см. раздел 2.3.2. Память выделяется в момент входа в функцию или блок и освобождается в момент выхода из функции или блока. При этом захват и освобождение памяти происходят практически мгновенно, т.к. компьютер только изменяет регистр, содержащий адрес вершины стека.

Локальные переменные можно использовать при рекурсии, поскольку при повторном входе в функцию в стеке создается новый набор локальных переменных, а предыдущий набор не разрушается. По этой же причине локальные переменные безопасны при использовании нитей в параллельном программировании (см. раздел 2.6.2). Программисты называют такое свойство функции реентерабельностью , от англ. re-enter able - возможность повторного входа. Это очень важное качество с точки зрения надежности и безопасности программы! Программа, работающая со статическими переменными, этим свойством не обладает, поэтому для защиты статических переменных приходится использовать механизмы синхронизации (см. 2.6.2), а логика программы резко усложняется. Всегда следует избегать использования глобальных и статических переменных, если можно обойтись локальными.

Недостатки локальных переменных являются продолжением их достоинств. Локальные переменные создаются при входе в функцию и исчезают после выхода из нее, поэтому их нельзя использовать в качестве данных, разделяемых между несколькими функциями. К тому же, размер аппаратного стека не бесконечен, стек может в один прекрасный момент переполниться (например, при глубокой рекурсии), что приведет к катастрофическому завершению программы. Поэтому локальные переменные не должны иметь большого размера. В частности, нельзя использовать большие массивы в качестве локальных переменных.

Динамическая память, или куча

Помимо статической и стековой памяти, существует еще практически неограниченный ресурс памяти, которая называется динамическая , или куча (heap ). Программа может захватывать участки динамической памяти нужного размера. После использования ранее захваченный участок динамической памяти следует освободить.

Под динамическую память отводится пространство виртуальной памяти процесса между статической памятью и стеком. (Механизм виртуальной памяти был рассмотрен в разделе 2.6.) Обычно стек располагается в старших адресах виртуальной памяти и растет в сторону уменьшения адресов (см. раздел 2.3). Программа и константные данные размещаются в младших адресах, выше располагаются статические переменные. Пространство выше статических переменных и ниже стека занимает динамическая память:

| адрес | содержимое памяти |

|---|---|

|

код программы и данные, защищенные от изменения |

|

| ... |

статические переменные программы |

| динамическая память | |

|

max. адрес (2 32 -4) |

стек |

Структура динамической памяти автоматически поддерживается исполняющей системой языка Си или C++ . Динамическая память состоит из захваченных и свободных сегментов, каждому из которых предшествует описатель сегмента. При выполнении запроса на захват памяти исполняющая система производит поиск свободного сегмента достаточного размера и захватывает в нем отрезок требуемой длины. При освобождении сегмента памяти он помечается как свободный, при необходимости несколько подряд идущих свободных сегментов объединяются.

В языке Си для захвата и освобождения динамической памяти применяются стандартные функции malloc и free , описания их прототипов содержатся в стандартном заголовочном файле " stdlib.h ". (Имя malloc является сокращением от memory allocate - "захват памяти".) Прототипы этих функций выглядят следующим образом:

void *malloc(size_t n); // Захватить участок памяти // размером в n байт void free(void *p); // Освободить участок // памяти с адресом p

Здесь n - это размер захватываемого участка в байтах, size_t - имя одного из целочисленных типов, определяющих максимальный размер захватываемого участка. Тип size_t задается в стандартном заголовочном файле " stdlib.h " с помощью оператора typedef (см. c. 117). Это обеспечивает независимость текста Си-программы от используемой архитектуры. В 32-разрядной архитектуре тип size_t определяется как беззнаковое целое число:

typedef unsigned int size_t;

Функция malloc возвращает адрес захваченного участка памяти или ноль в случае неудачи (когда нет свободного участка достаточно большого размера). Функция free освобождает участок памяти с заданным адресом. Для задания адреса используется указатель общего типа void* . После вызова функции malloc его необходимо привести к указателю на конкретный тип, используя операцию приведения типа, см. раздел 3.4.11. Например, в следующем примере захватывается участок динамической памяти размером в 4000 байтов, его адрес присваивается указателю на массив из 1000 целых чисел:

int *a; // Указатель на массив целых чисел. . . a = (int *) malloc(1000 * sizeof(int));

Выражение в аргументе функции malloc равно 4000 , поскольку размер целого числа sizeof(int) равен четырем байтам. Для преобразования указателя используется операция приведения типа (int *) от указателя обобщенного типа к указателю на целое число.

Пример: печать n первых простых чисел

Рассмотрим пример, использующий захват динамической памяти. Требуется ввести целое цисло n и напечатать n первых простых чисел. (Простое число - это число, у которого нет нетривиальных делителей.) Используем следующий алгоритм: последовательно проверяем все нечетные числа, начиная с тройки (двойку рассматриваем отдельно). Делим очередное число на все простые числа, найденные на предыдущих шагах алгоритма и не превосходящие квадратного корня из проверяемого числа. Если оно не делится ни на одно из этих простых чисел, то само является простым; оно печатается и добавляется в массив найденных простых.

Поскольку требуемое количество простых чисел n до начала работы программы неизвестно, невозможно создать массив для их хранения в статической памяти. Выход состоит в том, чтобы захватывать пространство под массив в динамической памяти уже после ввода числа n . Вот полный текст программы:

#include

Пример работы данной программы:

Введите число простых: 50 2 3 5 7 11 13 17 19 23 29 31 37 41 43 47 53 59 61 67 71 73 79 83 89 97 101 103 107 109 113 127 131 137 139 149 151 157 163 167 173 179 181 191 193 197 199 211 223 227 229

Операторы new и delete языка C++

В языке C++ для захвата и освобождения динамической памяти используются операторы new и delete . Они являются частью языка C++ , в отличие от функций malloc и free , входящих в библиотеку стандартных функций Си.

Пусть T - некоторый тип языка Си или C++ , p - указатель на объект типа T . Тогда для захвата памяти размером в один элемент типа T используется оператор new :

T *p; p = new T;

Например, для захвата восьми байтов под вещественное число типа double используется фрагмент

double *p; p = new double;

При использовании new , в отличие от malloc , не нужно приводить указатель от типа void* к нужному типу: оператор new возвращает указатель на тип, записанный после слова new . Сравните два эквивалентных фрагмента на Си и C++ .

Статическая оперативная память

Статическая память (SRAM) – это энергозависимая полупроводниковая память с произвольным доступом, в которой каждый разряд хранится в триггере, позволяющем поддерживать состояние разряда без постоянной перезаписи. Для организации чтения и записи из ячейки памяти дополнительно используется три или более транзисторов.

1. Устройство триггера.

Для того чтобы понять принцип работы статической памяти, обратимся к истокам схемотехники. И начнем с описания принципа работы триггера, изображенного на рисунке 1.

Триггер – это элемент памяти с двумя стабильными состояниями – «0» и «1». В установленном состоянии триггер сохраняется, пока на него подается питание.

Обычно триггер имеет два входа:

- R (Reset) – сбросить триггер (установить в состояние «0»),

- S (Set) – установить триггер в состояние «1»,

и два выхода: Q и инвертированное Q ().

Входы R и S используются для установки состояния триггера. Если на вход S подать напряжение, соответствующее логической единице (далее просто логическую единицу), а на вход R – напряжение, соответствующее логическому нулю (далее просто логический ноль), то триггер перейдет в состояние единицы и сохранит это состояние даже, если на вход S перестать подавать сигнал.

Если на вход S подать логический ноль, а на вход R – логическую единицу, то триггер перейдет в состоянии сохранения нуля.

При подаче на оба входа логического нуля, состояние триггера не измениться.

При подаче на оба входа логической единицы, в общем случае состояние триггера будет неопределенно, то есть неизвестно, в какое состояние он перейдет.

В таблице 1 приводится перечень всех возможных состояний триггера.

| S | R | Q i | Q i+1 | i | i+1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | ? | 1 | ? |

| 1 | 1 | 1 | ? | 0 | ? |

Таблица 1. Состояния триггера, в зависимости от сигналов на входе.

Рассмотрев логику работы триггера, давайте разберемся, как же он устроен. Структурная схема триггера приведена на рисунке 2.

Как видно из рисунка, состоит он из двух инвертеров (логических элементов «НЕ»), причем выход одного инвертера замкнут на вход другого.

Давайте рассмотрим, как же работают эти инвертеры при подаче различных сигналов на вход.

Первый случай, на вход S подана логическая единица, а на вход R – логический ноль, то есть установка триггера в единичное состояние. И так, если на вход S подать логическую единицу, то, пройдя через инвертер D.D2, она примет значение логического нуля. Таким образом, на выходе будет логический ноль. На вход R был подан логический ноль, в результате, на выходе инвертера D.D1 будет логическая единица, а, соответственно, на выходе Q будет так же логическая единица.

Если сигналы с входов снять (на вход S и R подать логический ноль), то состояние триггера не изменится. Логическая единица с выхода инвертера D.D1 пойдет на вход инвертера D.D2, а логический ноль с выхода D.D2 пойдет на вход инвертера D.D1, в результате чего на выходе инвертера D.D1 будет логическая единица. То есть мы замкнули цикл, который будет продолжаться до тех пор, пока будет на триггер подводиться питание. Зачем нужно питание, рассмотрим чуть позже, когда будем разбирать принцип устройства инвертера.

Рассмотрим второй случай, когда на вход S подан логический ноль, а на вход R –логическая единица, то есть сброс триггера. И так, если на вход S подать логический ноль, то, пройдя через инвертер D.D2, он примет значение логической единицы. Таким образом, на выходе будет логическая единица. На вход R была подана логическая единица, в результате, на выходе инвертера D.D1 будет логический ноль, а, соответственно, на выходе Q будет тот же логический ноль.

Так же, как и в первом случае, при снятии сигналов с входов R и S состояние триггера не изменится.

Давайте теперь более подробно рассмотрим принцип работы инвертера. Существуют различные способы организации инвертера, мы рассмотрим только один из них, самый простой. Этого будет вполне достаточно, чтобы понять принцип его организации. И так на рисунке 4 изображена структурная схема инвертера.

На рисунке представлена простейшая схема реализации инвертера, состоящая из одного транзистора. Давайте рассмотрим, как он работает.

На элемент всегда подается питание Uп. В результате, создаваемый ток может пойти либо по линии AB, в этом случае на выходе инвертера ток будет отсутствовать (будет логический ноль), либо – по линии AC, в этом случае на выходе инвертера ток будет присутствовать (будет логическая единица).

По линии AB ток пойдет, если транзистор VT1 будет открыт, а для этого необходимо подать напряжение на вход инвертера.

По линии AC ток пойдет, если транзистор VT1 будет закрыт, а это произойдет при отсутствии напряжении на входе инвертера.

Таким образом, если на вход инвертера подается логическая единица, то на выходе будет логический ноль. И, соответственно, при подаче на вход инвертера логического нуля, на выходе будет поучена логическая единица.

2. Устройство ячейки статической памяти.

Теперь, зная, как работает триггер и инвертер, рассмотрим устройство ячейки статической памяти и принцип ее работы. Естественно, рассматривать мы будем простейшую ячейку памяти. На практике используют множество дополнительных ухищрений для повышения скорости работы статической памяти. Но, зная принцип работы элементарной ячейки статической памяти, вы без особого труда в дальнейшем разберетесь и в принципе работы других реализаций ячеек статической памяти.

На рисунке 4 приведена упрощенная схема одного из способов организации ячейки статической памяти.

Как видите, она состоит из одного триггера и трех транзисторов, выполняющих роль ключей, открывающих и закрывающих доступ к ячейке памяти. Транзисторы VT1 и VT2 используются для разрешения и запрета записи в ячейку, а транзистор VT3 – для разрешения и запрета чтения.

Для записи данных необходимо подать напряжение в линию строки, после чего транзисторы VT1, VT2 и VT3 откроются. Затем для записи единицы необходимо подать напряжение, соответствующее логической единице, на линию D и напряжение, соответствующее логическому нулю, на линию . Для переключения триггера в состояние хранения нуля необходимо подать напряжение, соответствующее логическому нулю, на линию D и напряжение, соответствующее логической единице, на линию .

В установленном состоянии триггер будет оставаться даже после снятия напряжения с линии строки и с линий D и до тех пор, пока на него будет подаваться питание Uп.

Для считывания данных необходимо на выходы D и подать напряжение, соответствующее логическому нулю, так как подача двух логических нулей на входы триггера не изменит его состояния, а затем подать напряжение на строку. В результате, транзистор VT3 откроется, и ток с триггера по линии Q пройдет в устройство считывания. Одновременно с транзистором VT3 откроются транзисторы VT1 и VT2. Но так как напряжение на линиях D и соответствует логическому нулю, то оно не повлияет на состояние транзистора.

Считывание данных с ячейки статической памяти, в отличие от чтения с ячейки динамической памяти, не приводит к потере сохраненного бита данных, поэтому, перезапись данных в ячейку статической памяти не требуется.

3. Устройство микросхемы статической памяти.

Давайте перейдем к следующему этапу изучения работы статической памяти и рассмотрим ее общую логику работы. Для этого обратимся к упрощенной структурной схеме статической памяти, изображенной на рисунке 5.

Начнем с записи данных в статическую память и рассмотрим случай записи единицы в ячейку М 11 .

В контроллер шины памяти от контроллера памяти, встроенного в северный мост материнской платы или в процессор , приходит адрес ячейки памяти и данные для записи. Адрес ячейки преобразуется на две составляющие – номер строки и номер столбца. Номер строки передается в «Дешифратор адреса строки», откуда на нужную строку подается напряжение.

Так как мы рассматриваем запись в ячейку М 11 , то напряжение с дешифратора адреса строки подается на первую строку. В результате, транзисторы VT1, VT2 и VT3 открываются. Аналогичные транзисторы других ячеек памяти, располагающихся в этой строке, также открываются.

Через транзистор VT3 первой ячейки и аналогичные транзисторы других ячеек памяти первой строки пойдет ток, соответствующий состоянию триггеров этих ячеек, в «Буфер данных». Однако «Буфер данных» получаемую информацию будет игнорировать, так как у него нет сигнала от «Блока управления» на сохранение считываемых данных.

Параллельно с подачей напряжения на строку матрицы памяти с «Блока работы с данными» будет выдано напряжение, соответствующее записываемым данным, в «Блоки записи 1 - m», а с «Блока дешифровки адреса столбца» на соответствующие столбцы будет выдано разрешение (напряжение, соответствующее логической единице) на запись данных.

Блоки записи используются для запрета выдачи тока в линии D и при чтении данных и преобразования из входящих сигналов данных их инвертируемых сигналов для переключения состояния триггеров, в которые необходимо сохранить данные.

В нашем случае, запись проводится в ячейку М 11 , и записывается единица. Соответственно, с «Блока работы с данными» будет выдана логическая единица в «Блок записи 1», и с «Блока дешифровки адреса столбца» будет выдана логическая единица в «Блок записи 1».

Рассмотрим работу «Блока записи 1» при таких входных сигналах. И так, на входе элемента D.D3 будет логическая единица, а на выходе – логический ноль, так как элемент D.D3 – инвертер (логический элемент «НЕ»). Соответственно, на входах элемента D.D4 (логический элемент «И») будут: логический ноль и логическая единица. В результате, на выходе этого элемента будет логический ноль.

На входах элемента D.D5 (логический элемент «И») будут две логические единицы, в результате, на выходе этого элемента будет логический ноль.

Следовательно, на выходе D1 «Блока записи 1» будет напряжение, соответствующее логическому нулю, а на выходе 1 будет напряжение, соответствующее логической единице. Эти напряжения будут поданы на все ячейки памяти первого столбца. Однако у всех ячеек, кроме первой, транзисторы, разрешающие запись, закрыты, а, следовательно, подаваемое напряжение попадет только на триггер первой ячейки и переведет его в состояние хранения единицы.

После изменения состояния триггера первой ячейки напряжение с первой строки снимается, и транзисторы VT1, VT2 и VT3 закрываются, запрещая запись и чтение из ячейки.

При записи нуля в ячейку памяти все происходит по той же схеме, только с «Блока работы с данными» в «Блок записи 1» будет подано напряжение, соответствующее логическому нулю. Это значит, что на выходе D1 «Блока записи 1» будет напряжение, соответствующее логической единице, а на выходе 1 будет напряжение, соответствующее логическому нулю. Эти значения напряжений переведут триггер первой ячейки памяти в состояние хранения нуля.

В установленном состоянии триггер первой ячейки останется, пока на него будет подаваться питание Uп.

Чтение записи происходит еще проще. От контроллера памяти приходит адрес ячеек памяти, с которых требуется считать данные, и команда на чтение.

В результате, адрес преобразуется в номер строки, и на соответствующую строку будет подано напряжение, которое откроет транзисторы разрешения/запрета чтения/записи.

Рассмотрим случай, когда данные считываются из первой ячейки. В этом случае напряжение с «Дешифратора адреса строки» будет подано в первую строку, что приведет к открытию транзисторов VT1, VT2 и VT3 ячейки М 11 и всех остальных ячеек первой строки. Ток с триггера первой ячейки, через транзистор VT1, беспрепятственно пройдет в «Буфер данных». То же самое произойдет с остальными ячейками первой строки. Считанные с ячеек памяти первой строки данные сохранятся в «Буфере данных».

После того, как информация в «Буфере данных» будет сохранена, «Дешифратор адреса столбцов» выдаст номера столбцов, данные с которых необходимо считать, в «Буфер данных». Соответствующие данные будут переданы из микросхемы памяти в контроллер памяти, располагающийся в материнской плате или непосредственно в процессоре.

Для того чтобы при чтении данных не происходила запись в эти же ячейки, ведь транзисторы, разрешающие запись, открыты, блоки записи выдают в линии D и всех столбцов матрицы памяти напряжение, соответствующее логическому нулю. Это происходит из-за того, что с блока дешифровки адреса столбцов выдается напряжение, соответствующее логическому нулю на все «Блоки записи».

Как видите, работа статической памяти очень похожа на работу динамической памяти , однако процесс записи и чтения гораздо быстрее, так как не тратится время на заряд и разряд конденсаторов и не требуется регенерация ячеек. Однако необходимо обратить внимание, что рассмотренная нами схема сильно упрощена, и на практике используют гораздо более сложные механизмы записи и чтения из памяти, повышающие надежность и скорость работы статической памяти. Однако описанный выше принцип работы позволяет понять основы функционирования статической памяти, ее недостатки и преимущества. Давайте попробуем сформулировать их (основные недостатки и преимущества).

4. Достоинства и недостатки статической памяти.

Достоинства:

- высокая скорость работы;

- нет необходимости регенерации ячеек.

Недостатки:

- высокая цена;

- низкая плотность упаковки;

- небольшой объем;

- высокое энергопотребление.

В связи с перечисленными выше достоинствами и недостатками, область применения статической памяти ограничивается, в основном, использованием ее в качестве КЭШ-памяти, что позволяет при небольшом увеличении стоимости уменьшить влияние недостатков динамической памяти на производительность ЭВМ. Однако, это все лишь компромисс, позволяющий несколько сгладить разрыв в производительности процессора и памяти, и все вытекающие отсюда последствия.

Требуется кардинальное решение проблемы существующей с момента зарождения вычислительной техники. Существует множество экспериментальных разработок, позволяющих получить быструю и дешевую оперативную память, но многие из них пока существуют только в виде лабораторных образцов, многие имеют недостаточную надежность и так далее. Наиболее перспективный путь развития оперативной памяти – это использование магниторезистивной памяти, получающей все большее распространение.